Tous les Caps ont un circuit équivalent basé sur la chimie, la construction et la géométrie avec un minimum de composants ESR, C, Rleak, ESL indiqués ci-dessous. Certains ont des équiv ccts encore plus complexes. c'est pourquoi la substitution de cap doit tenir compte de l'application, du schéma, des notes de conception et de la mise en page pour éviter tout problème de choix.

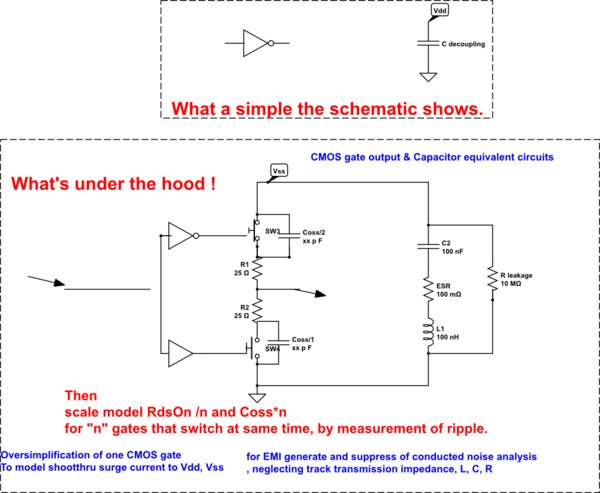

C'est la réalité de l'électronique lorsque les temps de montée à grande vitesse de commutation de déchargement de la capacité du commutateur CMOS doivent être supprimés pour améliorer les marges du signal par un découplage approprié de l'alimentation et de la terre.

C'est aussi la raison pour laquelle certaines personnes utilisent ECL et CML en raison du manque de pics de courant de la logique différentielle de mode actuel lorsqu'ils fonctionnent à des vitesses logiques extrêmes et ont besoin d'une immunité élevée au bruit.

Les MLCC mesurent généralement 2x1 LxW comme 1206, 603 402 et ont donc une certaine inductance basée sur cette taille. Mais généralement, la constante de temps est très faible par rapport aux électrolytiques lorsque vous utilisez la valeur ESR * C = T, ce qui signifie que la fréquence supérieure proche de 1 / T peut être beaucoup plus élevée pour le découplage ESR.

- les MLCC spéciaux à faible ESL utilisent LxW = 1x2 juste le contraire pour réduire l'inductance et ainsi augmenter le SRF, \ $ f = \ frac {1} {2 \ pi \ sqrt { LC}} \ $ créé par des sociétés telles que Murata et TDK.

Maintenant, lorsque vous mettez plusieurs bouchons 2x1 en parallèle de sorte que LxW devienne large de n, vous accomplissez la même chose en réduisant à L / n et en augmentant ainsi SRF de \ $ \ sqrt n \ $ tout en réduisant l'ESR de n pour que le résultat soit bien meilleur qu'un grand MLCC de même valeur uF. Une ESR trop faible peut également augmenter les pics de Q de SRF, lorsque plusieurs ESR C ultra faibles sont utilisés, alors lisez les détails de Murata TDK à ce sujet si vous ne comprenez pas encore.

Ceci est important, lorsque vous devez supprimer les pointes de courant de la logique CMOS avec des temps de montée > = 1ns qui ont une capacité de sortie Coss et 25 à 50 Ω RdsOn pour 74ALVCxx ou ARM uC ou à 50 Ω pour 74ALCxx CMOS. Le Coss augmente avec un RdsOn réduit dans les MOSFET mais diminue également avec la taille lithographique. Si vous imaginez un diviseur de capacité avec une tension commutée Vss, non seulement le rapport ESR / RdsOn est important, mais le net Coss / C (f) pour le découplage sur plusieurs décennies de f.

L'autre facteur est distribué Caps afin que l'inductance de la piste ne provoque pas de SRF plus faible que nécessaire et un emplacement plus proche du capuchon de découplage à la source réduit le bruit de pointe Vdd ET Vss. Le résultat est souvent une ondulation non seulement due à de mauvaises méthodes de sonde de l'oscilloscope, mais également à une fonction de transfert de pointe avec des fréquences de résonance et une réduction du rapport C et une réduction du rapport ESR. (Les deux sont des diviseurs de tension lorsque f < SRF))

simuler ce circuit - Schéma créé à l'aide de CircuitLab

Le temps de montée varie avec la famille CMOS et les pics de courant dépendent du nombre de commutateurs synchrones à l'intérieur du CI ou du groupe de CI