La mise à la terre de cette conception est très importante. Pour obtenir une bonne mise à la terre, il faut créer un chemin de retour à la terre pour que les "signaux de puissance" reviennent à leur source sur le même chemin qu'ils empruntent.

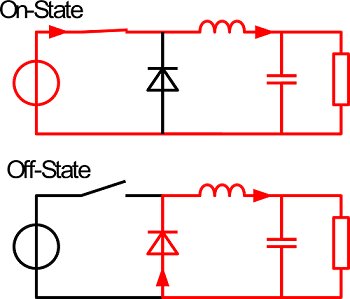

Si nous classions ces signaux de puissance, nous pourrions les séparer en deux groupes. Signaux de puissance "silencieux" et signaux de puissance "sauvages et bruyants". Comme j'ai essayé d'expliquer les signaux de puissance bruyants dans cette réponse, ces signaux doivent être pris avec grand soin. Dans un convertisseur abaisseur non synchrone typique, ces signaux comprennent ceux qui ont un grand changement de courant ou de tension entre les deux cycles du convertisseur abaisseur. Regardez le dessin ci-dessous;

Comme vous pouvez le voir, les signaux sauvages sont ceux qui changent de couleur. Ceux-ci incluent le chemin qui comprend la diode, ainsi que le chemin qui comprend le condensateur d'entrée et le commutateur. Dans votre configuration, qui est un convertisseur abaisseur synchrone, tout est pareil, sauf que vous changez la diode avec un autre commutateur.

Heureusement, ces commutateurs sont intégrés dans la puce que vous utilisez. Cela devrait donc donner un grand soulagement lors de la disposition du PCB.

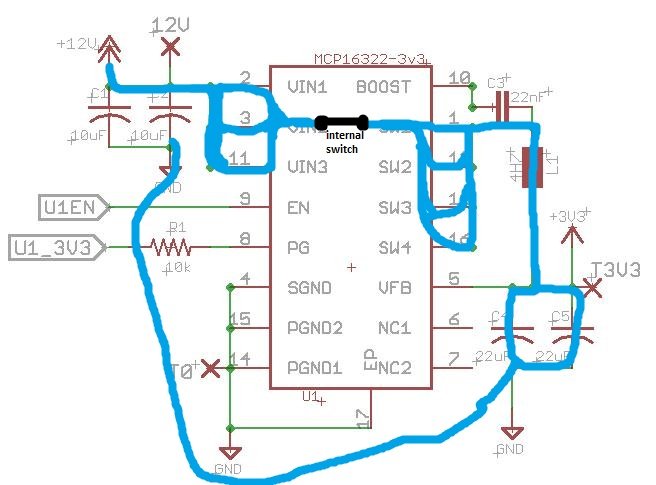

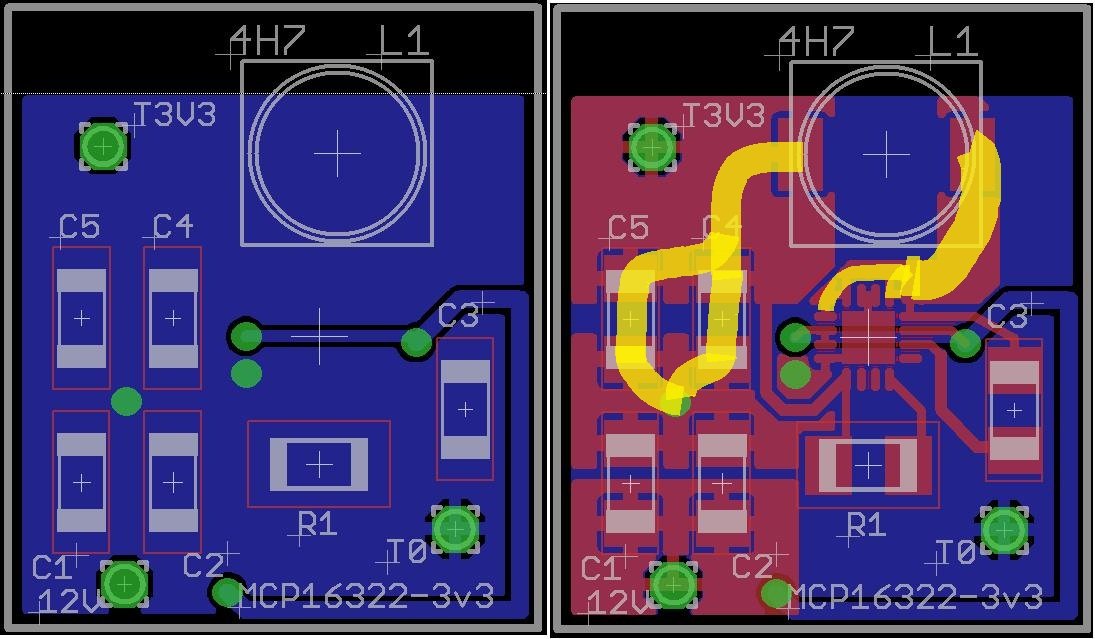

En venant à votre 3ème édition du design, soulignons ces chemins.

Lorsque l'interrupteur supérieur est sur ON, l'alimentation viendra de la source, allez à vos condensateurs d'entrée C1 et C2, puis allez dans les broches Vin de l'IC, qui sont 2,3 et 11. Ensuite, l'alimentation sortira des broches 1, 12, 13 et 16 et ira à l'inducteur, puis il ira au condensateur de sortie puis à la masse, et il essaiera de revenir en utilisant le même chemin.

Lorsque l'interrupteur supérieur est sur OFF, il y a de l'énergie stockée dans l'inductance lorsque l'interrupteur était sur ON, cette puissance dans l'inducteur commence à circuler de l'inductance aller au condensateur de sortie, aller à la terre, refluer vers les broches PGND du circuit intégré qui sont 14 et 15, puis il sortira du circuit intégré des broches 1 , 12, 13 et 16 puis retournent à sa source, c'est-à-dire l'inductance.

Dans le schéma que vous dessinez, voici les deux états du convertisseur:

ON State:

OFF State:

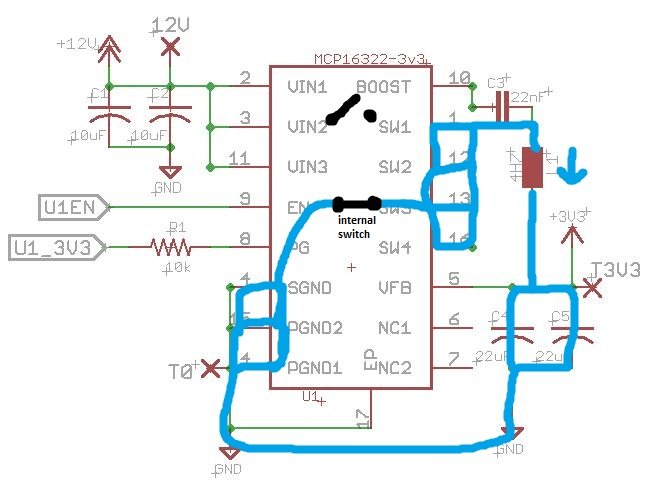

Dans le PCB que vous avez présenté, voici les deux états du convertisseur:

ON State:

État OFF:

Je suis très perplexe quant aux chemins de retour des signaux ici, donc si quelqu'un a une opinion, je le ferais soyez heureux d'entendre. Mais fondamentalement, supposons que les chemins de retour sont juste sous la trace. Si nous supposons cela, alors il n'y a aucun obstacle sur le chemin du retour à la maison.

Que peut-on faire?

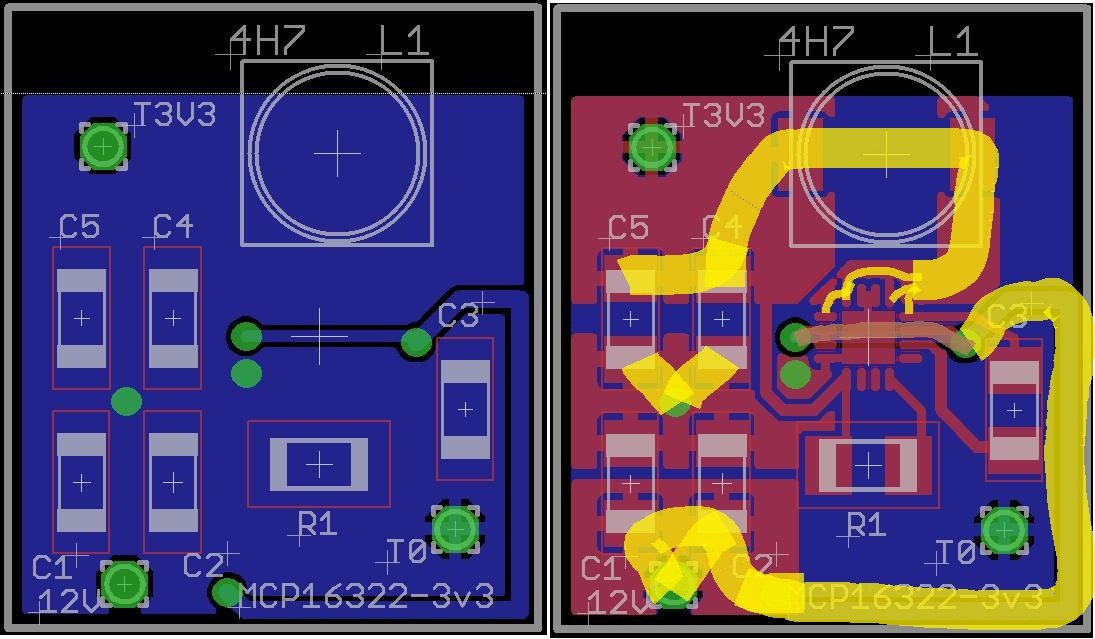

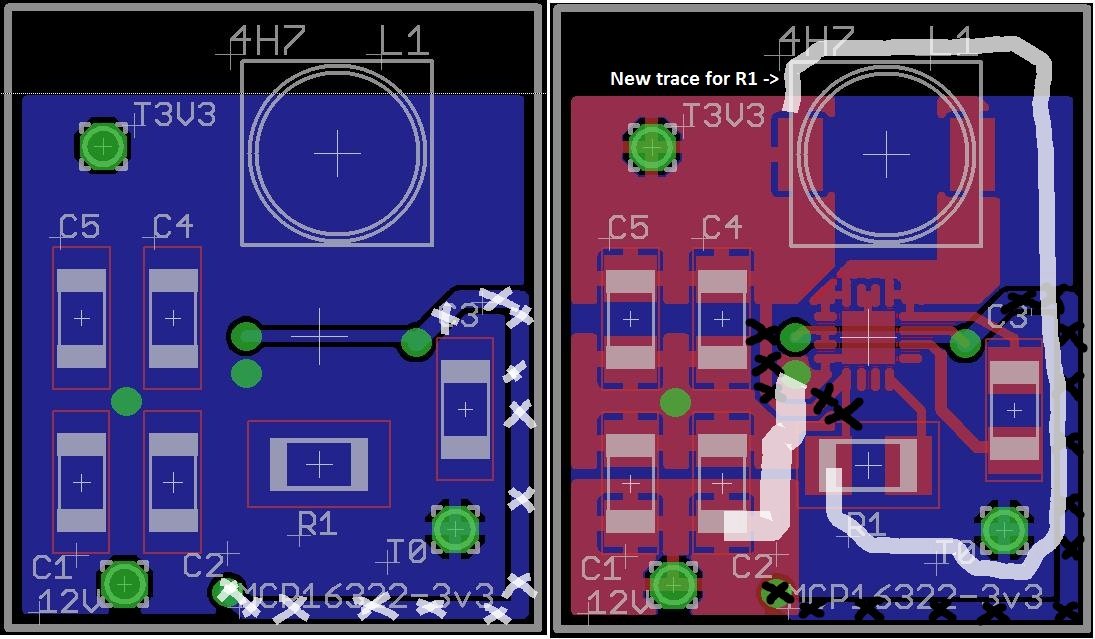

Je vois que votre conception est très similaire à la conception de référence sur la 22e page de la fiche technique, sauf que vous avez acheminé Cin différemment. De plus, vous avez acheminé différemment la connexion de R1 au rail 3.3V. Connectez R1 au rail 3,3 V comme ils l'ont fait dans la conception de référence. Ensuite, vous aurez de la place pour connecter Cin à l'IC avec une trace plus courte. J'ai essayé d'expliquer dans l'image ci-dessous. Vous pouvez augmenter le nombre de vias qui apporteront de meilleures connexions (plus faible impédance).

Bon article de TI: http: //www.ti .com / lit / an / snva054b / snva054b.pdf

Désolé pour le message inutilement long.